# Microprocessor Course

The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the product described any license under the patent rights of Motorola, Inc. or others.

Motorola reserves the right to change specifications without notice.

EXORciser, EXORdisk, EXORtape and EXORterm are trademark of Motorola Inc.

Motorola Inc. 1979

"All Rights Reserved"

# EUROPEAN MOTOROLA SEMICONDUCTOR SALES OFFICES

DENMARK Motorola A/S Bredebovej 23 DK-2800 Lyngby Tel. (02) 88 44 55

Motorola Semiconducteurs S.A. Headquarter 15-17, avenue de Ségur 75007 Paris Tel. 551 50 61

Sales Office 42, avenue de La Plaine-Fleurie 38240 Meylan (Grenoble) Tel. (76) 90 22 81

WEST GERMANY

EST GERMANY Motorola GmbH, Geschäftsbereich Halbleiter Headquarter Münchner Strasse 18 8043 Unterföhring Tel. (089) 92481

Tel. (089) 92-931 Sales Offices Hans-Böckler-Strasse 30 3012 Langenhagen — Hannover Tel. (0511) 77-20-37

8500 Nürnberg Tel. (0911) 6 57 61 Stralsunder Strasse 1 7032 Sindelfingen Tel. (07031) 8 30 74/8 30 75 Abraham-Lincoln-Strasse 28 6200 Wiesbaden Tel. (06121) 76 19 21

Motorola B.V. Emmalaan 41

ITALY Motorola S.p.A. Headquarter Via Ciro Menotti 11 20129 Milano Tel. 738 61 41/2/3 Sales Office Via Portanova 10 40123 Bologna — Tel. 26 69 05 Sales Office Via Costantino Maes 68 00162 Roma — Tel. 831 47 46

NORWAY Motorola A/B (Service Office) Brugt. 1 Oslo 1 — Tel. (02) 41 91 40

SOUTH AFRICA Motorola South Africa (Pty) Ltd. P.O. Box 39586 Bramley 2018 Tel. 786 1184

SWEDEN Motorola AB. Virebergsvaegen 19 17140 Solna – Tel. (08) 82 02 95

SWITZERLAND

Motorola Semiconductor Products S.A. Motorola Semiconductor Products S Alte Landstrasse 101 8702 Zollikon — Tel. (01) 65 56 56

UNITED KINGDOM

Motorpla Ltd. Headquarter York House, Empire Way Wembley Middlesex Tel. (01) 902 88 36 Sales Office 10-12, Mount Street, Television House Manchester M2 5WS, Lancs Tel. (61) 833 07 31/833 07 34 Sales Office

Colvilles Road, Kelvin Estate

East Kilbride, Scotland

Tel. (3552) 3 91 01

HEADQUARTERS EUROPEAN OPERATIONS

SWITZERLAND

Motorola Inc.

Semiconductor Products Group

16, chemin de la Voie-Creuse, P.O. Box 8

1211 Genéve 20

Tel. (022) 33 56 07

# FRANCHISED MOTOROLA SEMICONDUCTOR DISTRIBUTORS

AUSTRIA

Elbatex GmbH Endresstrasse 54 – 1238 Wien Tel. (222) 88 55 11

Diode Belgium Rue Picard 202-204 — 1020 Bruxelles Tel. (02) 428 51 05

DENMARK

Distributøren Interelko Aps Hovedgaden 16 – 4622 Havdrup Tel. (03) 38 57 16

FINLAND

Field Oy Veneentekijantie 18 – 00210 Helsinki 21 Tel. (80) 692 25 77

FRANCE

Bellion Electronique

Zone Industrielle de Kerscao/Brest

29219 Le Relecq-Kerhuon — B.P. 16

Tel. (98) 28 03 03

Celdis S.A. 53, rue Charles-Frérot — 94250 Gentilly Tel. (01) 581 00 20 tet. (017 981 00 20 Ets. F. Feutrier S.A. (Main Office) Rue des Trois-Glorieuses 42270 St-Priest-en-Jarez (St-Etienne) Tel. (77) 74 67 33

Ets. F. Feutrier S.A. Avenue Laplace — Zone industrielle 13470 Carnoux Tel. (42) 82 16 41

Tel. (42) 82 16 41 Feutrier II ed France 29, rue Ledru-Rollin — 92150 Suresnes Tel. (01) 772 46 A. (Main Office) 13, rue Victor-Hugo — BP 63 59350 Saint-André-lez-Lille Tel. (20) 51 21 33

Tel. (20) 51 21 33 Ets. Gros S.A. 14, avenue du Général-Leclerc — 54000 Nancy Tel. (83) 35 17 35

Tel. (83) 35 17 35 Ets. Gros A. 5, rue Pascal — 94800 Villejuif Tel. (01) 678 27 27 S.C.A.I.B. S.A. 80, rue d'Arcueil — Zone Silic 94150 Rungis Tel. (01) 687 23 13

iel. (al) 1687 23 13 Sté Commerciale Toutélectric (Main Office) 15-17, Bouvard Bonrepos – 31008 Toulouse Tel. (61) 82 11 33 Sté. Commerciale Toutélectric 80-83, quai des Queyres – 33100 Bordeaux Tel. (66) 86 50 31

Alfred Neye Enatechnik GmbH (Ab 1.1.1979) Schillerstrasse 14 — D-2085 Quickborn/Hamburg Tel. (04) 106 61 21 Distron oHG Distron oHG Beheimstrasse 3 1000 Berlin 10 Tel. (030) 342 10 41/45

EBV Elektronik Vertriebs-GmbH (Main Office) Gabriel-Max-Strasse 72

Gabriel-Max-Strasse 72 8000 München 90 Tel. (089) 64 40 55 EBV Elektronik Vertriebs GmbH In der Meineworth 9 3006 Burgwebel 1 / Hannover Tel. (051) 39 45 70

EBV Elektronik Vertriebs-GmbH Oststrasse 129 4000 Düsseldorf Tel. (0211) 8 48 46

EBV Elektronik Vertriebs-GmbH Myliusstrasse 54 6000 Frankfurt 1 Tel. (0611) 72 04 16

EBV Elektronik Vertriebs-GmbH Alexanderstrasse 63 7000 Stuttgart 1 Tel. (0711) 24 74 81

Jermyn GmbH Postfach 1180 6277 Camberg Tel. (06434) 60 05

Mütron Müller & Co. KG Bornstrasse 22

RTG, E. Springorum GmbH+ Co. (Main Office) Postfach 426 46 Dortmund 1 Tel. (0231) 5 49 51

RTG, E. Springorum GmbH+ Co. Friedrich-Ebert Damm 112 2000 Hamburg 70 Tel. (040) 693 70 61/62

RTG, E. Springorum GmbH+ Co. Ungererstrasse 43 8000 München 40 Tel. (089) 36 65 00

RTG, E. Springorum GmbH + Co. Reutlingerstrasse 87 7000 Stuttgart-Degerloch Tel. (0711) 76 64 28

RTG, E. Springorum GmbH+ Co. Mendelssohn-Bartholdy-Strasse 16 6200 Wiesbaden Tel. (06121) 52 73 09

SASCO Vertrieb von elektronischen Bauelementen GmbH (Main Office) Hermann-Oberth-Strasse 16 8001 Putzbrunn b. München Tel. (089) 46 40 61/69

SASCO Vertrieb von a Bauelementen GmbH Postfach 3066 4005 Düsseldorf/Meer Tel. (02150) 14 33

SASCO Vertrieb von elek Bauelementen GmbH Postfach 890214

3000 Hannover Tel. (0511) 86 25 86

SASCO Vertrieb von elektron Bauelementen GmbH Lorenzer Strasse 15 8500 Nürnberg Tel. (0911) 20 41 52

SASCO Vertrieb von elektronischen Bauelementen GmbH Stafflenbergstrasse 24 – 7000 Stuttgart 1 Tel. (0711) 24 45 21

SPOERLE Electronic (Ab 1.1.1979) Otto-Hahn-Strasse 13 — 6072 Dreieich b. Frankfurt Tel. (06103) \* 3 04-1

Technoprojekt (Main Office) Heinrich-Ebner-Strasse 13 7000 Stuttgart – Bad Cannstatt Tel. (0711) 56 17 12

Technoprojekt

Ostring 150 – 6231 Schwalbach/Ts

Tel. (06196) 8 21 00

Macedonian Electronics Ltd. Charilaou – P.O. Box 240 – Thessaloniki Tel. 30 68 00

Macedonian Electronics Ltd. Lloyd George 10 - Athe Tel. (21) 360 95 71

HOLLAND

B.V. Diode Hollantlaan 22 – Utrecht Tel. (030) 88 42 14

5473 ZG Heeswijk (N.B.) – P.O. Box 25 Tel. (41) 39 12 52

Interag Co., Ltd. XIII Rajk Laszlo u. 11 – P.O. Box 184

Milcom LTD, Motorola Building Niloo Street, Vanak Square — Teheran Tel. 66 12 14/15

Celdis Italiana S.p.A. (Main Office) Via F.IIi Gracchi 36 – 20092 Cinisello Balsamo (MI) Tel. (02) 612 00 41-2-3-4-5

Celdis Italiana S.p.A. Via Lorenzo il Magnifico 109 – 00162 Roma Tel. (06) 42 38 55

lei: (UB) 42:39 bb Celdis Italiana S.p.A. Via Turati, 33 – 40055 Castenaso (Bologna) Tel. (051) 78 – 80 78 Celdis Italiana S.p.A. Via Mombarcaro 96 – 10136 Torino Tel. (11) 35 93 12

Celdis Italiana S.p.A. Via Ognissanti, 83 – 35100 Padova Tel. (049) 2 68 02

Tel. (049) 2 68 02 Cramer Italia S.p.A. (Main Office) Via Cristoforo Colombo 134 – 00147 Roma Tel. (06) 51 79 81-2-3-4-5-6-7

Cramer Italia S.p.A. Via S. Simpliciano 2 – 20121 Milano Tel. (02) 80 93 26

Cramer Italia S.p.A. Via Umberto 1° 59 – 35100 Padova Tel. (049) 2 53 74

Cramer Italia S.p.A. Via Malta 5 – 40135 Bologna Tel. (051) 42 28 90 Tel. (051) 42 28 90 Cramer Italia S.p.A. Corso Traiano 28/15 — 10135 Torino Tel. (011) 619 20 62

Silverstar Ltd. S.p.A. Via dei Gracchi 20 – 20146 Milano Tel. (02) 49 96

Silverstar Ltd. S.p.A. Via Paisiello 30 – 00198 Roma Tel. (06) 844 88 41 Silverstar Ltd. S.p.A. Piazza Adriano 9 — 10139 Torino Tel. (011) 44 32 75/6 — 44 23 21

NIGERIA

Beckron International 14, Alhaji Bashorun Street SW Ikoyi – P.O. Box 1896 – Lagos Tel. 5 66 29

Ola Tandberg Elektro A/S Skedsmogatan 25 - Oslo 6 Tel. (02) 19 70 30

PHZ Transpol S.A. (Intraco Building)

UI. Stawki 2 — 00-950 Warsaw 1

Tel. (004822) 39 50 79

PORTUGAL

Equipamentos de Laboratorio LDA Rua Pedro Nunes 47 — Lisbon 1 Tel. 97 02 51

L'Electron 704 Main Pretoria Road, Wynberg Tul. P.O. Box 10544, Johannesburg 2000 Tel. 40 62 96

SPAIN

Hispano Electronica S.A. (Main Office)

Poligono Industrial "Urtinsa"

Apartado de Correos 48 — Alcorcón (Madrid)

Tel. (01) 619 41 08 Hispano Electronica S.A. Figols, 27-29 Barcelona 14 - Tel. 259 05 22/23

SWEDEN

/EDEN Interelko AB. Sandsborgsvägen 50 12233 Enskede – Tel. (08) 49 25 05 AB Gösta Bäckström Alströmergatan 22 – Box 12009 10221 Stockholm Tel. (08) 54 10 80

SWITZERLAND

Elbatex AG Alb. Zwyssig-Strasse 28 - 5430 Wettingen Tel. (056) 26 56 41 Omni Ray AG Dufourstrasse 56 – 8008 Zürich Tel. (01) 34 07 66

ERA Elektronik Sanyi Ve Ticaret A.S. Ankara Irtibat Bürosü Gazi Mustapha Kemal Bul. 12 KAT4D79 Yenisehir/Ankara — Tel. 25 49 33

UNITED KINGDOM

A.M. Lock & Co. Ltd Neville Street, Middletor Oldham, Lancs OL96LF Tel. (061) 652 04 31 Celdis Ltd. 37-39 Loverock Road Reading, Berks, RG3, 1ED Tel. (0734) 585 171

Cramer Components Ltd Hawke House Green Street Sunbury on Thames, Middlesex, England Tel. (9327) 8 55 77

Tel. (9327) 8 55 77 Crellon Electronics Ltd. 380, Bath Road Slough, Berks SLI 6 JE Tel. (06286) 6 36 11 ITT Electronic Services Edinburgh Way Harlow, Esex CM20 (2DF) Tel. Harlow (0279) 26 777 Jermyn Industries Vestry Estate – Sevenoaks, Kent Tel. (732) 5 11 74

Macro-Marketing Ltd. 396, Bath Road Slough, Berks SL1 6JD Tel. (06286) 630 11

YUGOSLAVIA

Elektrotehna Ljubljana Export-Import Titova 51 – P.O. Box 34-1 61000 Ljubljana Tel. (61) 32 02 41 Elektrotehna Ljubljan Filiala Beograd Marsala Tita 6/1 11000 Beograd Tel. (011) 69 69 24

# **EUROPEAN SEMICONDUCTOR FACTORIES**

FRANCE

Motorola Semiconducteurs S. Canto Laouzetto — Le Mirail 31023 Toulouse CEDEX Tel. (61) 40 11 88

GERMANY

Münchner Strasse 1 8043 Unterföhring Tel. (089) 92 481

UNITED KINGDOM

Motorola Semiconductors Ltd. Colvilles Road, Kelvin Estate East Kilbride/Glasgow (Scotland) Tel. (3552) 39 101

# **Table of contents**

|     |                              | Page |

|-----|------------------------------|------|

| 1.  | Number Systems               | 5    |

| 2.  | Microprocessing Unit         | 17   |

| 3.  | Memory                       | 39   |

| 4.  | Peripheral Interface Adapter | 45   |

| 5.  | ACIA                         | 67   |

| 6.  | Addressing Modes             | 83   |

|     | Assembler Techniques         | 93   |

| 8.  | Instruction Set              | 139  |

| 9.  | Program Problems             | 151  |

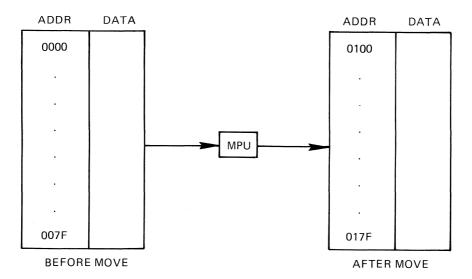

| 10. | Example Programs             | 171  |

| 11. | System Configuration         | 211  |

# **Number Systems**

#### NUMBER SYSTEM

The Motorola 6800 Microprocessor is an 8-bit system. It has 8 data lines, 16 address lines, and functions with 8- and 16-bit registers. It is, therefore, convenient to use the Hexadecimal Number System when interfacing with the M6800 system. However, before concentrating on the Hexadecimal Number System, a discussion of several other number systems would be beneficial.

The most familiar number system is Base 10 or Decimal—i.e., 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9—since this is the system in general use. What does a typical base-10 number represent? Take, for example, 2743. The number  $2743_{10}$  really represents  $3 \times 10^0 + 4 \times 10^1 + 7 \times 10^2 + 2 \times 10^3$ ; and, as can be seen, the least significant digit (LSD) is 3 and the most significant digit (MSD) is 2.

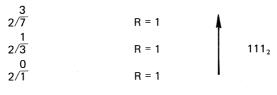

In digital computers, numbers are represented in base 2 or binary form, i.e., 1's and 0's. One method of converting base 10 numbers to binary numbers is known as "repeated division by 2". Using  $47_{10}$  for example:

Converting 1011112 back to a base-10 number, we have:

$$101111_{2} = 1 \times 2^{0} + 1 \times 2^{1} + 1 \times 2^{2} + 1 \times 2^{3} + 0 \times 2^{4} + 1 \times 2^{5}$$

$$= 1 \times 1 + 1 \times 2 + 1 \times 4 + 1 \times 8 + 0 \times 16 + 1 \times 32$$

$$= 1 + 2 + 4 + 8 + 0 + 32$$

$$= 47_{10}$$

In general, converting from a number in any base to a number in base 10 is accomplished as follows:

$$(A_0B^0 + A_1B^1 + A_2B^2 + A_3B^3 + A_4B^4 + ... + A_nB^n)$$

where B is the base of the number system and A is the particular digit in the original number corresponding to its position to the left of the decimal point. On the example just completed, (101111).

$$A_0 = 1$$

,  $A_1 = 1$ ,  $A_2 = 1$ ,  $A_3 = 1$ ,  $A_4 = 0$ , and  $A_5 = 1$  and  $B = 2$  (base 2).

# N-2 Number System

Another number system used with digital computers is octal, or base 8, since octal is a more convenient way of representing binary 2. To illustrate, the conversion of 61 in base 10 to a number in base 8 and a number in base 2 using the method of repeated division is shown below:

| 8/61<br>0<br>8/7     | R = 5 LSD<br>R = 7 MSD | 75 <sub>8</sub><br>(Octal) |

|----------------------|------------------------|----------------------------|

| <br>30<br>2/61       | R = 1 LSB              |                            |

| 15<br>2/30           | R = 0                  |                            |

| 2/15                 | R = 1                  | 1111012                    |

| 3<br>2/ <del>7</del> | R = 1                  | (Binary)                   |

| $\frac{1}{2/3}$      | R = 1                  |                            |

| $\frac{0}{2/1}$      | R = 1 MSB              |                            |

As a proof that  $75_8$  =  $111101_2$ , convert each digit of 75 base 8 to base 2 by continuous division.

Convert 7<sub>8</sub> to base 2:

Convert  $5_8$  to base 2:

This demonstrates that an octal number (base 8) can be used to easily represent a string of binary bits (base 2). Therefore,  $75_8$  =  $111101_2$  which is the same pattern of 1s and 0s as derived by converting from base 10 to base 2.

As previously mentioned, the M6800 Microprocessor utilizes 8- and 16-bit registers. But when trying to use the octal number system, there is a slight problem. Since in octal each digit represents 3 binary bits, and 8 and 16 bits cannot be selected evenly into groups of 3. This is resolved with the hexadecimal number system. Hexadecimal is a base-16 number system and can be handled in exactly the same manner

as base 8 or base 2. In Hexadecimal, four bits (in binary) represent one Hexadecimal number. Thus, an 8-bit register can be represented by a 2-digit hex number. To illustrate, assume there exists the binary number 01100111 in an 8-bit register. If this bit pattern is divided into two 4-bit groups of 0110 and 0111, then the hex representation would be 67<sub>16</sub>. The following is offered as a proof:

1100111<sub>2</sub> =

$$1 \times 2^{0} + 1 \times 2^{1} + 1 \times 2^{2} + 0 \times 2^{3} + 0 \times 2^{4} + 1 \times 2^{5} + 1 \times 2^{6} + 0 \times 2^{7}$$

MSB LSB =  $1 + 2 + 4 + 0 + 0 + 32 + 64 + 0$

=  $103_{10}$

and LS Digit (LS half-byte)

$$67_{16} = 7 \times 16^{0} + 6 \times 16^{1}$$

MS Digit (MS half-byte)

=  $7 \times 1 + 6 \times 16$

=  $7 + 96$

=  $103_{10}$

Therefore,  $67_{16} = 01100111_{2} = 103_{10}$

From this simple example, one might wonder how hexadecimal digits (base 16) are represented for numbers above 9. The following table shows the solution to this dilemma.

| Base 10   | Base 16       |

|-----------|---------------|

| (Decimal) | (Hexadecimal) |

| 0         | 0             |

| 1         | 1             |

| 2         | 2             |

| 3         | 3             |

| 4         | 4             |

| 5         | 5             |

| 6         | 6             |

| 7         | 7             |

| 8         | 8             |

| 9         | 9             |

| 10        | Α             |

| 11        | В             |

| 12        | С             |

| 13        | D             |

| 14        | E             |

| 15        | F             |

Table I

### N-4 Number System

To convert any decimal (base 10) number to hexadecimal (base 16), again use the repeated division method. As an example, convert  $1023_{10}$  to hexadecimal.

therefore,  $1023_{10} = 3FF_{16}$ . As a check, convert  $3FF_{16}$  back to a base 10 number.

$$3FF_{16} = 15 \times 16^{0} + 15 \times 16^{1} + 3 \times 16^{2}$$

$$= 15 \times 1 + 15 \times 16 + 3 \times 256$$

$$= 15 + 240 + 768$$

$$= 1023_{10}$$

To further elaborate on the relationship between hexadecimal and binary, convert  $1023_{10}$  to binary and then back to hexadecimal. First,  $1023_{10}$  to binary:

| 511                | D 4   | L CD:+ |             |   |

|--------------------|-------|--------|-------------|---|

| 2/1023             | R = 1 | LSBit  |             |   |

| 255<br>2/511       | R = 1 |        |             |   |

| 127<br>2/255       | R = 1 |        |             |   |

| 63<br>2/127        | R = 1 |        |             | * |

| 31<br>2/63         | R = 1 |        | 11111111111 |   |

| 1 <u>5</u><br>2/31 | R = 1 |        |             |   |

| $\frac{7}{2/15}$   | R = 1 |        |             | • |

| 3                  |       |        |             |   |

| 2/7                | R = 1 |        |             |   |

| $\frac{1}{2/3}$    | R = 1 |        |             |   |

| 0                  |       |        |             |   |

| 2/1                | R = 1 | MSBit  |             |   |

Now, arranging this number into three groups of four bits each and then converting each group to its hexadecimal counterpart, the result is  $1023_{10}$ , represented in hexadecimal 1111111111<sub>2</sub> = 0011 1111 1111<sub>2</sub> =  $3FF_{16}$ . Where  $0011_2 = 3_{16}$  and  $1111_2 = F_{16}$  (from Table 1).

In summary, remember that each hexadecimal (base 16) digit is a representation of 4 binary bits. It is easy to convert from hex to binary and binary to hex. For convenience, a limited conversion chart follows.

<sup>\*</sup>From Table I.

# **CONVERSION CHART**

| Decimal  | Octal    | Hexadecimal | Binary                 |

|----------|----------|-------------|------------------------|

| 0<br>1   | 0        | 0           | 0000 0000<br>0000 0001 |

| 2        | 2<br>3   | 2<br>3      | 0000 0010<br>0000 0011 |

| 4        | 4        | 4           | 0000 0100              |

| 5<br>6   | 5<br>6   | 5<br>6      | 0000 0101<br>0000 0110 |

| 7        | 7        | 7           | 0000 0111              |

| 8        | 10       | 8           | 0000 1000              |

| 9<br>10  | 11<br>12 | 9<br>A      | 0000 1001<br>0000 1010 |

| 11       | 13       | В           | 0000 1011              |

| 12       | 14       | С           | 0000 1100              |

| 13<br>14 | 15<br>16 | D<br>E      | 0000 1101<br>0000 1110 |

| 15       | 17       | F           | 0000 1111              |

| 16<br>17 | 20<br>21 | 10<br>11    | 0001 0000<br>0001 0001 |

| 18       | 22       | 12          | 0001 0001              |

| 19       | 23       | 13          | 0001 0011              |

| 20<br>21 | 24<br>25 | 14<br>15    | 0001 0100<br>0001 0101 |

| 22       | 26<br>26 | 16          | 0001 0101              |

| 23       | 27       | 17          | 0001 0111              |

| 24<br>25 | 30<br>31 | 18<br>19    | 0001 1000<br>0001 1001 |

| 26<br>26 | 32       | 19<br>1A    | 0001 1001              |

| 27       | 33       | 1B          | 0001 1011              |

| 28<br>29 | 34<br>35 | 1C<br>1D    | 0001 1100<br>0001 1101 |

| 30       | 36       | 1E          | 0001 1101              |

| 31       | 37       | 1F          | 0001 1111              |

| 32<br>33 | 40<br>41 | 20<br>21    | 0010 0000<br>0010 0001 |

| 34       | 42       | 22          | 0010 0001              |

| 35       | 43       | 23          | 0010 0011              |

| 36<br>37 | 44<br>45 | 24<br>25    | 0010 0100<br>0010 0101 |

| 37<br>38 | 45<br>46 | 26          | 0010 0101              |

| 39       | 47       | 27          | 0010 0111              |

| 40       | 50       | 28          | 0010 1000              |

# Two's Complement

The M6800 system does not do direct subtraction, so the method of 2's complement addition is used to accomplish the subtraction. The 2's complement of any binary number is its additive inverse. That is, a binary number plus its 2's complement always equals zero. Or,

How is the 2's complement of a binary number computed? There are several methods. One way of calculating the 2's complement is to take the number to be converted, invert all the digits, then add one.

For example, find the 2's complement of 01011011.  $(91_{10})$

Therefore, 10100101 is the 2's complement of 01011011.

The following are examples of subtraction by the method of 2's complement addition:

1. Given 61-12 = ? (base 10), or

|      | Binary Notation.  | mex inotation |

|------|-------------------|---------------|

| 61 = | 00111101          | 3D            |

| - 12 | - <u>00001100</u> | - <u>0C</u>   |

But to do the subtraction, first convert 00001100 ( $12_{10}$ ) to a 2's complement number.

| Therefore, given |        | Binary Notation       | <b>Hex Notation</b> |

|------------------|--------|-----------------------|---------------------|

|                  |        | 00001100              | OC .                |

| a.               | Invert | 11110011              | F3                  |

| b.               | Add    | + 0000001             | + 01                |

|                  |        | 11110100 2's compleme | nt F4               |

So the subtraction becomes 2's complement addition

$$\begin{array}{c} 00111101 & 3D \\ + 11110100 & + F4 \\ \hline \text{ans} & 00110001 & \text{ans} & 31 \\ \end{array}$$

As a check

$$\begin{array}{l}

61_{10} \\

-\frac{12_{10}}{49_{10}} = 00110001_2 = 31_{16}

\end{array}$$

Hex Notation

2. Given 61-2=? (base 10)

|                                   | Dinary rectation       | TION HOLDER         |

|-----------------------------------|------------------------|---------------------|

| 61                                | 00111101               | 3D                  |

| - 2                               | 0000010                | - 02                |

| Doing the 2's complement addition |                        |                     |

|                                   | <b>Binary Notation</b> | <b>Hex Notation</b> |

|                                   | 00111101               | 3D                  |

**Binary Notation**

For further information see page 1-21 of the M6800 Microprocessor Applications Manual  $\,$

<sup>\*2&#</sup>x27;s complement of 00000010

<sup>\*\*</sup> Hex notation of 2's complement

# 8-BIT 2'S COMPLEMENT

| DECIMAL | BINARY    | HEXADECIMAL |

|---------|-----------|-------------|

| +127    | 0111 1111 | 7F          |

| •       | •         | •           |

| •       | •         | •           |

| •       | •         | •           |

| +64     | 0100 0000 | 40          |

| •       | •         | •           |

| •       | •         | •           |

| •       | •         |             |

| +2      | 0000 0010 | 02          |

| +1      | 0000 0001 | 01          |

| 0       | 0000 0000 | 00          |

| -1      | 1111 1111 | FF          |

| 2       | 1111 1110 | FE          |

| •       | •         | •           |

| •       | •         | •           |

| •       | •         | •           |

| -64     | 1100 0000 | C0          |

| •       | •         | •           |

| •       | •         | •           |

| •       | •         | •           |

| -127    | 1000 0001 | 81          |

| 128     | 1000 0000 | 80          |

|         |           |             |

# Homework - Number Systems

Convert the following base 10 numbers to base 2 and base 16. Prove each base 2 and base 16 number is equal to its original base 10 number.

|    | Decimal              | Binary | Hexadecimal |

|----|----------------------|--------|-------------|

| a) | 9210                 |        |             |

| b) | 14410                |        |             |

| c) | 409110               |        |             |

| d) | 254 <sub>10</sub>    |        |             |

| e) | 256 <sub>10</sub>    |        |             |

| f) | 64,522 <sub>10</sub> |        |             |

| g) | 200010               |        |             |

Convert the following decimal numbers to 8-bit 2's complement representation.

| h) | - 17 <sub>10</sub> |  |

|----|--------------------|--|

| i) | +2510              |  |

| j) | $-5_{10}$          |  |

| k) | - 128              |  |

Turn this page over to check your answers.

# N-10 Number System

# Answers

|     | Decimal | Binary                  | Hexadecimal  |

|-----|---------|-------------------------|--------------|

| a)  | 92      | 1011100                 | 5C           |

| b)  | 144     | 10010000                | 90           |

| c)  | 4091    | 111111111011            | FFB          |

| d)  | 254     | 11111110                | FE           |

| e)  | 256     | 10000000                | 100          |

| f)  | 64522   | 1111110000001010        | FCOA         |

| g)  | 2000    | 11111010000             | 7D0          |

|     |         |                         |              |

|     | Decimal | 8-Bit 2's Complement Re | presentation |

| h)  | - 17    | 11101111                |              |

| i)  | +25     | 00011001                |              |

| i)  | -5      | 11111011                |              |

| k)  | -128    | 1000000                 |              |

| ••• | 0       |                         |              |

# **MPU**

# MICROPROCESSING UNIT (MC6800)

#### Introduction

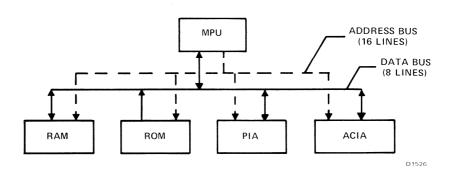

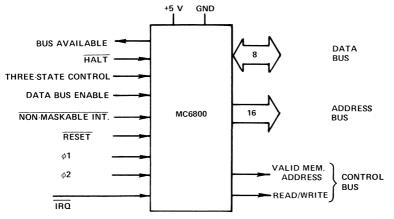

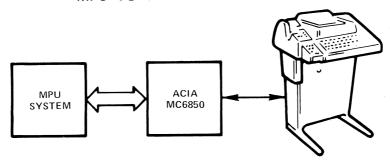

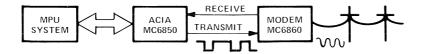

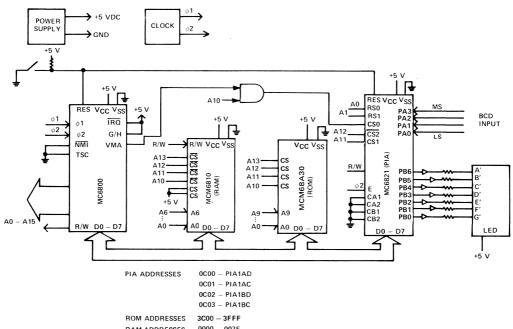

The Motorola M6800 Microcomputer System of standard LSI (Large Scale Integration) devices permits the systems designer to configure and connect a total system with a minimum amount of time and effort. The MC6800 Microprocessing Unit (MPU) forms the nucleus of the system. LSI circuits available which may be used to configure a total system in conjunction with the MC6800 MPU include: 1) MCM6810 Random Access Memory (RAM), 2) MCM6830 Read Only Memory (ROM), 3) MC6821 Peripheral Interface Adapter (PIA), and 4) MC6850 Asynchronous Communications Interface Adapter (ACIA).

The MPU communicates with the rest of the system via a 16-bit address bus and an 8-bit data bus. The 16-bit address bus provides the MPU with the capability of addressing up to 64K. The 8-bit data bus is bidirectional in that data is transferred both into the MPU or out of the MPU over the same bus. A read/write (R/W) line is provided to allow the MPU to control the direction of data transfer. Since the same bus is used both for data into the MPU and out of the MPU, a separate 8-line bus is saved.

Other features of the M6800 system include a single +5 volt supply, operation at clock rates from 100 kilohertz to 1 megahertz, plus hardware and software interrupt-capability.

# MICROPROCESSING UNIT (MC6800)

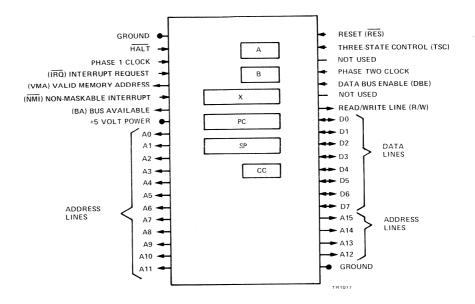

The nucleus of the M6800 Microcomputer Family is the microprocessing unit (MPU). The MPU is enclosed in a 40-pin package as shown on the following page.

## Features included in the MPU are:

- 1. Two accumulators (A and B)

- 2. One index register (X)

- 3. One program counter register (PC)

- 4. One stack pointer register (SP)

- 5. One condition code register (CC)

- 6. 72 instructions

- 7. Six addressing modes

- 8. System clock range of 100 kilohertz to 1 megahertz

- 9. Program interrupt capability

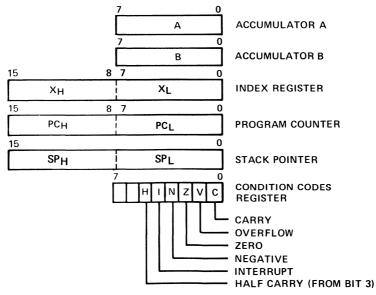

# **ACCUMULATORS**

The MPU contains 2 accumulators designated A and B. Each accumulator is 8 bits (one byte) long and is used to hold operands and data from the arithmetic logic unit.

## INDEX REGISTER

The index register (X) is a 16-bit (2 byte) register which is primarily used to store a memory address in the indexed mode of memory addressing. The index register may be decremented, incremented, and stored.

#### PROGRAM COUNTER

The program counter (PC) is a 16-bit register that contains the address of the next byte to be fetched from memory. When the current value of the program counter is placed on the address bus, the program counter will be incremented automatically.

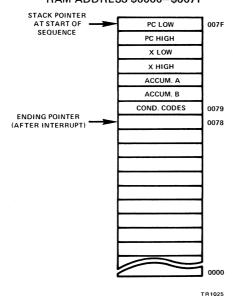

#### STACK POINTER

The stack pointer (SP) is a 16-bit (2 byte) register that contains a beginning address, normally in RAM, where the contents of the MPU registers may be stored when the MPU has other functions to perform such as an interrupt or a Subroutine. The address in the stack pointer is the starting address of sequential memory locations in RAM where MPU contents of the registers will be stored. The contents of the MPU will be stored in the RAM as follows:

Stack Point Address : contents of PCL

Stack Pointer Address—1 : contents of PCH

Stack Pointer Address—2 : contents of XL

Stack Pointer Address—3 : contents of XH

Stack Pointer Address—4 : contents of A

Stack Pointer Address—5 : contents of B

Stack Pointer Address—6 : contents of CC

After the contents of each register is stored on the stack, the stack pointer will be decremented. When the stack is unloaded (contents of registers restored), the contents of the last register on the stack will be the first register that is restored.

# CONDITION CODE REGISTER (CC)

The condition code register is an 8-bit register. Each *individual* bit may be set or cleared by execution of an instruction. To see how each instruction affects the condition code register, refer to the M6800 programming manual. This register is used by the conditional branch instructions. Bits 6 and 7 are not used and remain at logic "1".

Carry-Borrow For addition, the carry-borrow condition code (C) in the zero-bit position, represents a carry. This bit gets set (C = 1) to indicate a carry,

and is reset (C = 0), if there is no carry.

Overflow The V-bit (bit 1) of the condition code register is set (V = 1) when two's complement overflow results from an arithmetic operation, and is

reset (V = 0), if two's complement overflow does not occur.

Zero The Z-bit (bit 2) of the condition code register is set (Z = 1), if the result of an arithmetic operation is zero, and is reset (Z = 0), if

the result is not zero.

# CONDITION CODE REGISTER С Н Z CARRY/BORROW OVERFLOW (2'S COMP.) ZERO RESULT NEGATIVE $(b_7 = 1)$ INTERRUPT MASK

# BITS SET AS A RESULT OF PREVIOUS OPERATION!

| ABA:              | A=<br>B=   | 1000 1000<br>1000 1000                                           | A+B=    | 1 0001 0000         | ; | H = 1, Z = 0<br>C = 1, N = 0<br>V = 1                            |

|-------------------|------------|------------------------------------------------------------------|---------|---------------------|---|------------------------------------------------------------------|

| DEC A             | <b>A</b> = | 0000 0001                                                        | A-1=    | 0000 0000           | ; | Z = 1, N = 0                                                     |

| LDA A             | = \$8      | 0                                                                | A=      | 1000 0000           | ; | N = 1, Z = 0, V = 0                                              |

| COM A<br>OR DEC A | <b>A</b> = | 1000 0000 ,                                                      | Ā=      | 0111 1111           |   | N = 0, V = 0, C = 1, Z = 0<br>N = 0, V = 1, C = UNCHANGED, Z = 0 |

| АВА               |            | 1000 0010 = -126 <sub>10</sub><br>1000 0010 = -126 <sub>10</sub> | A+B = [ | 1 0000 0100<br>+410 | ; | V = 1, $Z = 0C = 1$ , $N = 0H = 0$ TR1022                        |

The N-bit (bit 3) of the condition code register is set (N = 1), if bit 7 Negative

of any operation is set (equal to 1). The N-bit is reset (N = 0), if bit 7 of

HALF-CARRY (b3 →b4)

any result is equal to 0.

Interrupt

If this bit is set (I = 1), IRQ interrupts are inhibited. If I = 0, the processor may be interrupted by IRQ being in the low state. The I bit is set Mask

via SEI instruction or by an interrupt occurring (IRQ, NMI, or SWI). This bit is cleared with RTI (assuming I bit was clear before interrupt)

or CLI.

The half-carry bit H (bit 5) of the condition code register is set (H = 1)Half-Carry during execution of any of the instructions ABA, ADC, or ADD, if

there is a carry from bit position 3 to bit position 4. The half-carry is reset (H = 0) during these operations, if there is no carry from bit

position 3.

The information the condition code register holds is the results of the NOTE:

instruction that last affected the condition code register.

#### MPU Signal Descriptions

# READ/WRITE (R/W)

This output line is used to signal all devices external to the MPU that the MPU is in a read state (R/W = high) or a write state (R/W = low). The normal standby state of this line when no external devices are being accessed is a high state. This line is three state. When three state control goes high, this line enters the high-impedance mode.

2. VALID MEMORY ADDRESS (VMA)

This output line (when in the high state), tells all devices external to the MPU that there is a valid address in the address bus. This signal *is not three state*.

3. DATA BUS ENABLE (DBE)

This signal will enable the data bus drives when in the high state. This input is normally the phase 2 ( $\phi$ 2) clock. During the high state, it will permit data to be output during a write cycle. During an MPU read cycle, the data bus drives will be disabled internally.

4. INTERRUPT

REQUEST (IRQ)

(Level Sensitive Pin)

This input requests that an interrupt sequence be generated. The processor will wait until it completes the current instruction that is being executed before it recognizes the request. At that time, if the interrupt mask bit in the condition code register is not set (interrupt masked), the machine will begin an interrupt sequence. The index register, program counter, accumulators, and condition code register are stored on the stack. Next the MPU will respond to the interrupt request by setting the interrupt mask bit high so that no further interrupts may occur. At the end of the cycle, a 16-bit address will be loaded that points to a vectoring address which is located in memory locations n-6 and n-7. Where n is the highest ROM address. An address loaded at these locations causes the MPU to jump to an interrupt routine in memory.

5. PHASE ONE  $(\phi 1)$  AND PHASE TWO  $(\phi 2)$  CLOCKS

These two pins are used for a two-phase, non-overlapping clock that runs at the  $V_{DD}$  voltage level. These clocks run at a rate up to 2 MHz for MC68B00.

6. RESTART (RES)

This input is used to start the MPU from a power-down condition, resulting from a power failure or an initial start-up of the processor. If a positive edge is detected on the input, this will signal the MPU to begin the restart sequence. This will restart the MPU and start execution of a routine to initialize the processor. All the higher order address lines will be forced high.

# MPU-6 Microprocessing Unit (M6800)

For the restart, the last two memory locations in the last ROM (n and n-1) will be accessed, whereby an address is stored which is the address to be loaded in the program counter which tells the processor where program execution is to begin.

# 7. NONMASKABLE INTERRUPT (NMI) (Edge Sensitive Pin)

This input requests that a nonmask-interrupt sequence be generated within the processor. As with the Interrupt Request signal, the processor will complete the current instruction that is being executed before it recognizes the NMI signal. The interrupt mask bit in the condition code register has no effect on NMI. However, NMI does set the Interrupt Mask bit.

The index register, program counter, accumulators, and condition code register are stored away on the stack. At the end of the cycle, a 16-bit address will be loaded that points to a vectoring address which is located in memory locations n-2 and n-3. An address loaded at these locations causes the MPU to jump to a non-maskable interrupt routine in memory.

# 8. GO/HALT (G/H)

When this input is in the high state, the machine will fetch the instruction addressed by the program counter and start execution. When low, all activity in the machine will be halted. This input is level sensitive. In the halt mode, the machine will stop at the end of instruction. Bus Available will be at a logic "1" level Valid Memory Address will be at a logic "0" and all other three-state lines will be in the three-state mode.

The halt line must go low with the leading edge of phase one to insure single instruction operation. If the halt line does not go low with the leading edge of phase one, one or two instruction operations may result, depending on when the halt line goes low relative to the phasing of the clock.

# 9. BUS AVAILABLE (BA)

The Bus Available signal will normally be in the low state. When activated, it will go to the high state indicating that the MPU has stopped and that the address bus is available. This will occur if the Go/Halt line is in the halt (low) mode or the MPU is in a "wait" state as the result of some instruction such as the WAI instruction.

# 10. THREE-STATE CONTROL (TSC)

This input causes all of the address lines and the Read/Write line to go into the off or high-impedance state. The Valid Memory Address and Bus Available signals will be forced low. The data bus is not affected by TSC and has its own enable (Data Bus Enable). In DMA applications, the Three-State Control line should be brought high on the leading edge of the Phase One Clock. The  $\phi 1$  clock must be held in the high state for this function to operate properly. The address bus will then be available for other devices to directly address memory. Since the MPU is a dynamic device, it must be refreshed periodically, or destruction of data will occur.

# 11. ADDRESS BUS (AØ/A15)

Sixteen pins are used for the address bus. The outputs are three-state bus drivers capable of driving one standard TTL load and 90 pF at 2 megahertz. When the output is turned off, it is essentially an open circuit. This permits the MPU to be used in DMA applications.

# 12. DATA BUS (DØ/D7)

Eight pins are used for the data bus. It is bidirectional, transferring data to and from the memory and peripheral devices. It also has three-state output buffers capable of driving one standard TTL load and 130 pF at 2 megahertz.

Now that we have talked about the pins of the MPU package, we will talk about the "heartbeat" of the system—the clock.

### The MPU Clock

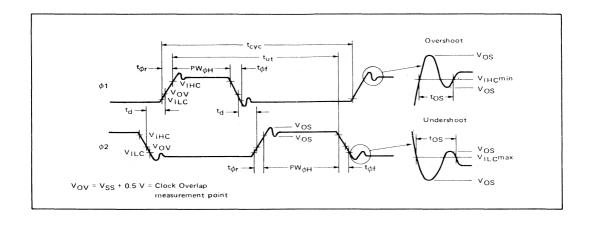

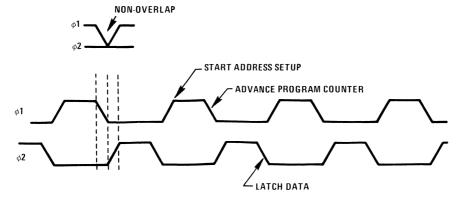

The MPU clock driver must meet the minimum and/or maximum criteria. These criteria are explained by the table accompanying the timing waveform. (See MPU-10.) The information to remember is that on the falling edge of  $\phi$ 1, the program counter is advanced, and, on the falling edge of  $\phi$ 2, the data is latched into the MPU.

| 1                            | 2               | 3                                                             | 4                   | 5          |

|------------------------------|-----------------|---------------------------------------------------------------|---------------------|------------|

| Program<br>Memory<br>Address | Opcode/<br>Data | Comments                                                      | Addressing<br>Modes | Mnemonic   |

| 1000<br>1001                 | 86<br>05        | LDA A with<br>Hex 05                                          | Immediate           | LDA A #\$5 |

| 1002<br>1003                 | D6<br>F1        | LDA B with the contents of F1=04 (hex)                        | Direct              | LDA B \$F1 |

| 1004                         | 1B              | Add contents of Accum B to contents of Accum A and store in A | Accumulator         | ABA        |

Up to this point we have physically described the microprocessor, i.e., the accumulators and registers. We will now explain how this microprocessor works. This will be easier if we use a small program to trace the flow of data through the MPU system.

The program shown on MPU-7 will be used; and, in conjunction with MPU-8, a description of the operation of the MPU will be described.

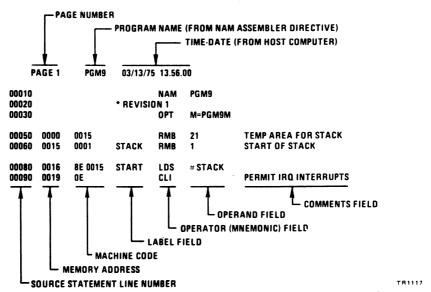

The program shown above is divided into 5 columns. Column 1 is the Program Memory Address column. Here we show the address locations where the program is stored. Column 2 contains the instruction opcode or data. This information is in hexademical notation. Column 3 is a comment column to aid you in understanding what task is to be performed. Column 4 describes the addressing mode used. More information is contained in the addressing mode section. The fifth column gives the mnemonic for the particular instruction used.

When Phase 1 ( $\phi$ 1) goes high, the contents of the program counter are transferred to the address bus. While this action is taking place, VMA will go to a logic 1 indicating a valid address. On the falling edge of  $\phi$ 1, the program counter will be incremented (if required) by one. When Phase 2 ( $\phi$ 2) goes high, data is placed on the data bus; and, during the falling edge of  $\phi$ 2, the data is latched into the MPU. This sequence occurs every time the MPU addresses a memory location and data is moved.

Let us return to the program and begin with  $\phi1$  going to a logic 1. The contents of the program counter (we will assume to be 1000 hex)\* will be transferred to the to the address bus.  $\phi1$  goes low and the program counter is incremented to 1001. Memory location 1000 has been selected; and, when  $\phi2$  goes to a logic 1, its contents will be transferred to the data bus. Looking at our program on MPU-7, we see that the data stored in memory location 1000 is 86. Therefore, 86 is the data transferred to the data bus. Again, during the falling edge of  $\phi2$ , the data on the bus is latched into the MPU.

# PROGRAMMING MODEL OF THE MICROPROCESSING UNIT

TR10

<sup>\*</sup>All addresses will be given in hexademical notation.

# **EXECUTABLE INSTRUCTIONS — ALPHABETIC LIST**

| ABA | ADD ACCUMULATORS                | INS | INCREMENT STACK POINTER                     |

|-----|---------------------------------|-----|---------------------------------------------|

| ADC | ADD WITH CARRY                  | INX | INCREMENT INDEX REGISTER                    |

| ADD | ADD                             | JMP | JUMP                                        |

| AND | LOGICAL AND                     | JSR | JUMP TO SUBROUTINE                          |

| ASL | ARITHMETIC SHIFT LEFT           |     |                                             |

| ASR | ARITHMETIC SHIFT RIGHT          | LDA | LOAD ACCUMULATOR                            |

| BCC | BRANCH IF CARRY CLEAR           | LDS | LOAD STACK POINTER                          |

| BCS | BRANCH IF CARRY SET             | LSR | LOAD INDEX REGISTER                         |

| BEQ | BRANCH IF EQUAL TO ZERO         | NEG | LOGICAL SHIFT RIGHT<br>NEGATE               |

| BGE | BRANCH IF GREATER OR EQUAL ZERO | NOP | NO OPERATION                                |

| BGT | BRANCH IF GREATER THAN ZERO     |     |                                             |

| BHI | BRANCH IF HIGHER                | ORA | INCLUSIVE OR ACCUMULATOR                    |

| BIT | BIT TEST                        | PSH | PUSH DATA                                   |

| BLE | BRANCH IF LESS OR EQUAL         | PUL | PULL DATA                                   |

| BLS | BRANCH IF LOWER OR SAME         | ROL | ROTATE LEFT                                 |

| BLT | BRANCH IF LESS THAN ZERO        | ROR | ROTATE RIGHT                                |

| BMI | BRANCH IF MINUS                 | RTI | RETURN FROM INTERRUPT                       |

| BNE | BRANCH IF NOT EQUAL TO ZERO     | RTS | RETURN FROM SUBROUTINE                      |

| BPL | BRANCH IF PLUS                  |     |                                             |

| BRA | BRANCH ALWAYS                   | SBA | SUBTRACT ACCUMULATORS                       |

| BSR | BRANCH TO SUBROUTINE            | SBC | SUBTRACT WITH CARRY                         |

| BVC | BRANCH IF OVERFLOW CLEAR        | SEC | SET CARRY                                   |

| BVS | BRANCH IF OVERFLOW SET          | SEI | SET INTERRUPT MASK                          |

| CBA | COMPARE ACCUMULATORS            | SEV | SET OVERFLOW                                |

| CLC | CLEAR CARRY                     | STA | STORE ACCUMULATOR                           |

| CLI | CLEAR INTERRUPT MASK            | STS | STORE STACK REGISTER                        |

| CLR | CLEAR                           | STX | STORE INDEX REGISTER                        |

| CLV | CLEAR OVERFLOW                  | SUB | SUBTRACT                                    |

| CMP | COMPARE                         | SWI | SOFTWARE INTERRUPT                          |

| COM | COMPLEMENT                      | TAB | TRANSFER ACCUMULATORS                       |

| CPX | COMPARE INDEX REGISTER          | TAP | TRANSFER ACCUMULATORS TO CONDITION CODE REG |

| DAA | DECIMAL ADJUST                  | TBA | TRANSFER ACCUMULATORS                       |

| DEC | DECREMENT                       | TPA | TRANSFER CONDITION CODE REG TO ACCUMULATOR  |

| DES | DECREMENT STACK POINTER         | TST | TEST                                        |

| DEX | DECREMENT INDEX REGISTER        | TSX | TRANSFER STACK POINTER TO INDEX REGISTER    |

|     |                                 | TXS | TRANSFER INDEX REGISTER TO STACK POINTER    |

| EOR | EXCLUSIVE OR                    | WAI | WAIT FOR INTERRUPT                          |

| INC | INCREMENT                       |     |                                             |

|     |                                 |     | 7040-4                                      |

TR1090

|                                                                                                            | MC6800                            | Min |         | Max  |    |

|------------------------------------------------------------------------------------------------------------|-----------------------------------|-----|---------|------|----|

| Clock Timing (Figure 1) Cycle Time                                                                         | t <sub>cyc</sub>                  | 1.0 | -       | 10   | μς |

| Clock Pulse Width $(\text{Measured at V}_{CC} - 0.3 \text{ V}) \hspace{1cm} \phi \text{1,}  \phi \text{2}$ | ${\sf PW}_{\phi{\sf H}}$          | 400 |         | 9500 | ns |

| Total $\phi$ 1 and $\phi$ 2 Up Time                                                                        | t <sub>ut</sub>                   | 900 | . –     | _    | ns |

| Rise and Fall Times $$\phi {\rm 1},\phi {\rm 2}$$ (Measured between VSS + 0.3 V and VCC $-$ 0.3 V)         | t <sub>φr</sub> , t <sub>φf</sub> |     | -       | 100  | ns |

| Delay Time or Clock Separation (Measured at $V_{OV} = V_{SS} + 0.6 V$ )                                    | <sup>t</sup> d                    | 0   | active. | 9100 | ns |

| Overshoot Duration                                                                                         | tos                               | 0   | -       | 40   | ns |

# MPU CLOCK WAVE FORM

TR1018

This information will be decoded as an opcode versus data, since it will be assumed the last instruction was terminated.

Looking at MPU-7, we see that LDA A requires 2 cycles and 2 bytes of data. The first cycle was used to bring in the first byte of data, 86, into the MPU. On the next  $\phi$ 1 cycle, the program counter is transferred to the address bus and 1001 is placed on the address bus selecting memory location 1001.  $\phi$ 1 now falls and the program counter is incremented by 1 to 1002,  $\phi$ 2 rises to a logic 1 and 05 is the data placed on the data bus.  $\phi$ 2 goes low and 05 is now latched into the A accumulator. Here we have used the immediate mode of addressing. In the immediate mode of addressing, the data is contained in the second byte of the instruction.  $\phi 1$  goes high and the program counter transfers its contents to the address bus which is 1002.  $\phi$ 1 goes low and the program counter is incremented to 1003 hex.  $\phi$ 2 goes high and D6 is the data placed on the data bus. Since the MPU finished the previous instruction (2 cycles, 2 bytes), it now knows that the next data D6 is an opcode. To accomplish this instruction we need 3 cycles and 2 bytes of data. We have used 1 cycle and 1 byte of data fetching the opcode. Now  $\phi 1$  goes high and the contents of the program counter (1003) is transferred to the address bus.  $\phi$ 2 goes high and F1 is now placed on the data bus.  $\phi$ 2 falls and F1 is latched into the MPU. Notice that we have used the direct mode of addressing. This mode of addressing can be used when addressing memory locations 0 through 255 decimal. In this mode, the second byte of data is an address.

To review, in the direct mode, the first byte is the opcode and the second byte is the address. Finally, on the third cycle, the data at memory location F1 is transferred to the B accumulator. On this last cycle, the program counter does not have to and will not increment.  $\phi1$  now goes high and the program counter transfers 1004 hex to the address bus.  $\phi1$  goes low and the program counter is incremented to 1005 hex.  $\phi2$  goes high and 1B is placed on the data bus; and, on the falling edge of  $\phi2$ , 1B is latched into the MPU. To complete this instruction we need 2 cycles and 1 byte of data. The mode of addressing we have used here is the accumulator mode. In this mode of address the opcode and operand are contained in the first byte of data. All that that is needed to terminate this instruction is another cycle to add the contents of accumulator B to the contents of accumulator A. After this cycle has been completed, accumulator A has 09 hex and accumulator B has 04.

Any program can be handled in this fashion. Refer to a copy of the instruction set summary chart. By looking at the mnemonic, you can obtain the hex opcode for the addressing mode used. The required number of cycles and bytes are also given so you can "step" through a particular program.

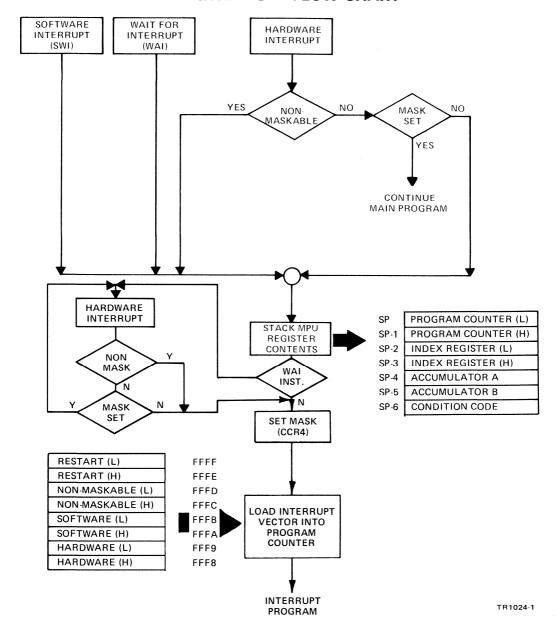

#### HARDWARE INTERRUPTS

What happens when the MPU gets a hardware interrupt? After it has been determined that the interrupt is not nonmaskable, the MPU checks the status of the mask bit (bit 4 of the condition code register). If the mask bit is set, the main program continues until a CLI (clears bit 4 of condition code register) instruction is executed, after which time the MPU will honor an interrupt by going to the stack pointer (SP) register and will fetch an address which will be the first address in RAM where the status of the MPU registers will be stored during servicing of the interrupt.

SP contents of program counter low SP-1 contents of program counter high SP-2 : contents of index register low SP-3 contents of index register high SP-4 contents of accumulator A SP-5 contents of accumulator B : SP-6 contents of condition code register

The address in the stack pointer register is determined by the programmer.

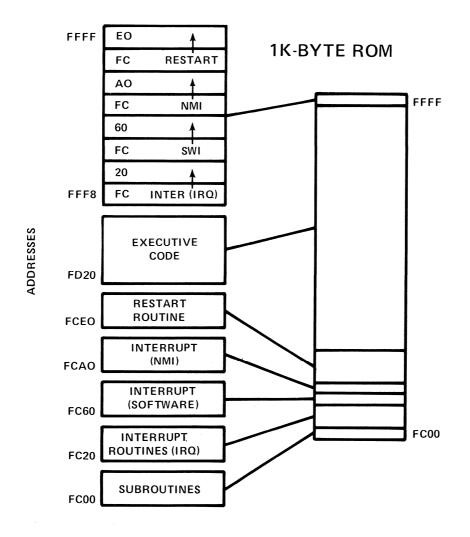

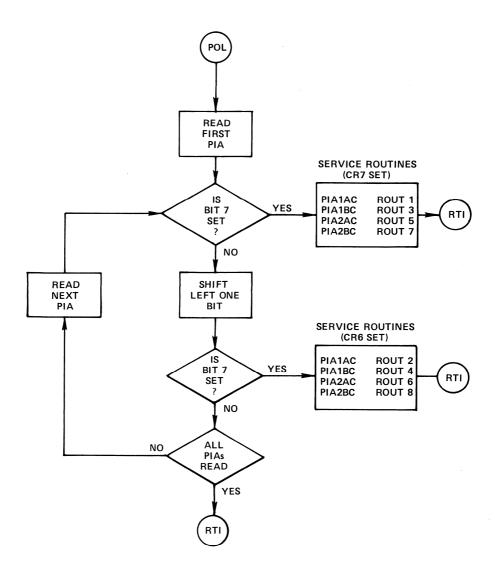

After the contents of the MPU registers have been stored in the stack, the mask bit is set, thus preventing any further interrupts from interfering with the MPU until the program executes a CLI instruction. Next the MPU hardware automatically looks at addresses FFF8 (MS) and FFF9 (LS) for the address of the polling routine to find out where the interrupt came from and what action to take.

After the interrupt has been serviced and an RTI instruction is executed, the stack—which contains the contents of the registers before the interrupt—is unloaded in reverse order, i.e., the condition code register is loaded first, then accumulator B is restored, etc. When the registers have been restored to their contents before the interrupt, the processor continues as though nothing happened.

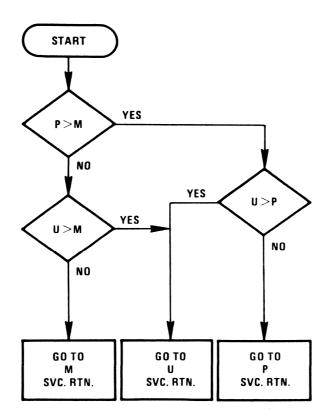

The total story of interrupts is shown on the opposite page in the form of a flow chart.

# SUMMARY OF MPU OPERATION

The MPU requires a two-phase, symmetrical, nonoverlapping clock. During the first phase of the clock ( $\phi$ 1 high), an address will be placed on the address bus by the MPU. During the second phase of the clock ( $\phi$ 2 high), the bidirectional data bus will be active. The first byte of an instruction enters the MPU and is transferred into an internal instruction register and decoded by the MPU. The MPU will then contain the information needed to read in an additional one or two bytes of program as necessary. Once the entire instruction is read into the MPU (one, two, or three bytes), the instruction is then executed. The MPU then reads in the next sequential byte in the program and places it again in the instruction register. The program will sequentially be executed in this manner unless a branch or jump instruction changes the value of the program counter. If this occurs, the next instruction to be executed is determined by the new program counter value.

# **INTERRUPT FLOW CHART**

## MPU-14 Microprocessing Unit (M6800)

If an interrupt or reset occurs during this process, the program counter value will also be changed. The new program counter value is determined by the highest eight memory locations that are reserved for reset and interrupt vectors.

In the case of interrupt, the stack pointer is used to store the contents of the internal registers necessary to return to the program location prior to the interrupt. This happens when the interrupt program exits by an RTI (Return from Interrupt instruction). Similarly, the stack pointer is used to store the program counter value when a JSR (Jump to Subroutine) or BSR (Branch to Subroutine) instruction occurs. The program counter returns to its original value when an RTS (Return from Subroutine) instruction occurs. The stack pointer value is set by an LDS (Load Stack Pointer) instruction.

# RESET SEQUENCE (Figure TR1029, below)

- 1. While  $\overline{\text{HALT}}$  is high,  $\overline{\text{Reset}}$  goes low for at least eight cycles of  $\phi 1$ ,  $\phi 2$ , during which interrupt bit (I) in CC is set.

- 2. Data at FFFE loads into PCH.

- 3. Data at FFFF loads into PCL.

- 4. PC contents go out on address bus during  $\phi$ 1.

- 5. Contents of memory location addressed enters instruction register during  $\phi 2$  and is decoded as first instruction.

- If two or more byte instruction, additional bytes enter MPU for execution. If not, go to next step.

- 7. After execution, step 5 is repeated for subsequent instructions.

# **IRQ** SEQUENCE

- If the I bit in condition code register is not set (I = 0) and IRQ goes low, the IRQ sequence will be entered.

- 2. After completion of the current intruction, internal registers PC, X, A, B, and CC will be stored in RAM at the address indicated by the stack pointer in descending locations (7 bytes in all).

- 3. The IRQ mask (bit I = 1) is set.

- 4. Data at FFF8 gets loaded into PCH.

- 5. Data at FFF9 gets loaded into PCL.

- 6. PC contents go out on address bus during  $\phi$ 1.

- 7. Contents of memory location addressed enters instruction register during  $\phi 2$  and is decoded as first instruction of interrupt routine.

- 8. If it is a more than 1 byte instruction, additional bytes enter MPU for execution. If not, go to next step.

- 9. After execution, step 7 is repeated for subsequent instructions. This loop is repeated until the instruction "RTI" is executed.

### NMI SEQUENCE

- 1. If NMI goes low, the MPU will wait for completion of current instruction.

- 2. The internal registers PC, X, A, B, and CC will then be stored in RAM at the address indicated by the stack pointer in descending locations (7 bytes in all).

- 3. The IRQ (bit I = 1) mask is set.

- 4. Data at FFFC is loaded into PCH.

- 5. Data at FFFD is loaded into PCL.

- 6. PC contents go out on address bus during  $\phi$ 1.

- 7. Contents of memory location addressed enters instruction register during  $\phi 2$  and is decoded as first instruction of NMI subroutine.

## MPU-16 Microprocessing Unit (M6800)

- If two or more byte instruction, additional bytes enter MPU for execution. If not, go to next step.

- 9. After execution, step 7 is repeated for subsequent instructions. This loop is repeated until the instruction RTI is executed.

# **RTI EXECUTION**

- 1. The contents of the stack are loaded back into the MPU (unwinds).

- The contents of the PC go out on the address bus to fetch the first byte of the next instruction.

# SWI INSTRUCTION

- 1. Contents of the MPU registers PC, X, A, B, and CC are stored in RAM at the address indicated by the stack pointer in descending location (7 bytes in all).

- 2. The  $\overline{IRQ}$  mask (bit I = 1) is set.

- 3. Data at FFFA gets loaded into PCH.

- 4. Data at FFFB gets loaded into PCL.

- 5. PC contents go out on address bus during  $\phi$ 1.

- 6. Contents of memory location addressed enters instruction register during  $\phi 2$  and is decoded as first instruction of SWI subroutine.

- 7. If it is a more than one byte instruction, additional bytes enter MPU for execution. If not, go to next step.

- 8. After execution, step 6 is repeated for subsequent instructions. This loop is repeated until the instruction RTI is executed.

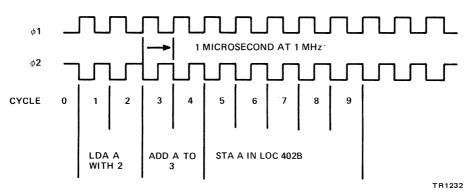

# CYCLE BY CYCLE DESCRIPTION OF SAMPLE PROGRAM

| ROM Address | ROM Content | Instruction  |  |  |

|-------------|-------------|--------------|--|--|

|             |             |              |  |  |

| 0018        | 86          | LDA A #2     |  |  |

| 0019        | 02          |              |  |  |

| 001A        | 8B          | ADD A #3     |  |  |

| 001B        | 03          |              |  |  |

| 001C        | В7          | STA A \$402B |  |  |

| 001D        | 40          |              |  |  |

| 001E        | 2B          |              |  |  |

<sup>#</sup> indicates immediate mode of addressing.

NOTE: Address 402B may be a RAM, PIA, or ACIA.

# **DESCRIPTION OF PROGRAM**

The A accumulator is loaded with the number 2. Then the number 3 is added to the 2 in the A accumulator with the result of 5 left in the A accumulator. The 5 in the A accumulator is then stored in location 402B.

<sup>\$</sup> indicates a hex number.

# Cycle-by-Cycle Description of Sample Program

#### CYCLE

#### DESCRIPTION

- 0 The program counter is assumed to be set at 0018.

- 1 The program counter is gated onto the Address Bus (AØ-A15) and the read/write (R/W) line is put in a high state corresponding to a read condition. This results in ROM address 0018 being accessed and the contents of this address (86) being loaded into the instruction register (IR). The program counter has incremented and becomes 0019. The byte "86" in the IR is decoded and interpreted to be a load A immediate (LDA A IMM) instruction.

- The program counter is gated onto the Address Bus and the R/W line is set high corresponding to a read condition. This accesses ROM address 0019 with the contents of this address (02) being put on the Data Bus (D0-D7). Since the instruction was decoded to be an LDA A immediate, the "02" is loaded into the A accumulator. The program counter has incremented and becomes 001A.

- The sequence in (1) is repeated except ROM address 001A is accessed resulting in 8B being loaded into the instruction register, and decoded to be an ADD A immediate. The program counter has incremented to 001B.

- 4 The sequence in (2) is repeated except the data "03" is added to the A accumulator giving a result in the A accumulator of "05". The program counter has incremented to 001C.

- The sequence in (1) is repeated which results in B7 being loaded into the instruction register. The program counter has incremented to 001D. The instruction register is decoded and determined to be a STA A extended. This causes the MPU to interpret the next two sequential locations in memory (001D and 001E) as a 16-bit address with 001D the most significant and 001E the least significant half of the address.

- 6 The number (40) in ROM address 001D is read by the MPU and saved. The program counter has incremented to 001E.

- 7 The contents of ROM address 001E (2B) is read by the MPU and saved. The MPU now has a full 16-bit address saved of 402B. The program counter has incremented to 001F.

- 8 The extended address of 402B is gated onto the address bus register, and the Data Bus is gated to output the A accumulator to the addressed memory location.

- 9 Address 402B is accessed and the R/W line is put in a low state, corresponding to a write. The data in the A accumulator is then gated onto the data bus and stored in location 402B.

TR1028

| SS               | COMMENTS  LOAD ACC.A WITH HEX NO. 5  (DATA)  LOAD ACC.B WITH DATA STORED  AT MEM. LOCATION 2004 | MODES  | MNEMONIC    |

|------------------|-------------------------------------------------------------------------------------------------|--------|-------------|

|                  | LOAD ACC.A WITH HEX NO. 5 (DATA) LOAD ACC.B WITH DATA STORED AT MEM. LOCATION 2004              | CLIVER |             |

|                  | (DATA) LOAD ACC.B WITH DATA STORED AT MEM. LOCATION 2004                                        | MMED   | LDAA #\$5   |

|                  | LOAD ACC.B WITH DATA STORED AT MEM. LOCATION 2004                                               |        |             |

|                  | AT MEM. LOCATION 2004                                                                           | EXTND  | LDAB \$2004 |

|                  | \VU V_\VU                                                                                       | *      |             |

|                  | (DALA UA)                                                                                       |        |             |

|                  | ADD CONT. OF B ACC TO A ACC                                                                     | INHER  | ABA         |

|                  | AND STORE IN A ACC.                                                                             |        |             |

|                  | STORE CONT. OF A ACC. (OF)                                                                      | BIR    | STAA \$50   |

|                  | IO MEMORY LOCATION 50                                                                           |        |             |

|                  | LOAD THE INDEX REGISTER                                                                         | IMMED  | 08\$#XQ7    |

|                  | WITH THE HEX NUMBER 80                                                                          |        |             |

|                  |                                                                                                 |        |             |

|                  | LOAD THE A ACC. WITH THE                                                                        | OXONI  | LDAA \$5,X  |

|                  | DATA STORED AT THE MEM. LOC.                                                                    |        |             |

|                  | INDEX REG + 5(85)                                                                               |        |             |

| -                | INCREMENT THE INDEX REG                                                                         | INHER  | XNI         |

|                  | BY 1 (80 → 81)                                                                                  |        |             |

| INUE SC          | COMPARE THE INDEX REGISTER                                                                      | IMMED  | V8\$# Xd0   |

| ▶ 100F 00        | WITH THE HEX NUMBER 8A                                                                          |        |             |

| 1010 8A          |                                                                                                 |        |             |

| 1011 26          | IF COMPARISON IS NOT EQUAL                                                                      | BEL    | BNE [LABEL] |

| <b>■</b> 1012 F8 | BRANCH BACK TO LOAD A ACC                                                                       |        |             |

|                  | (100B)                                                                                          |        |             |

| 1013 8E          | OTHERWISE LOAD STACK POINTER                                                                    | IMMED  | LDS #\$7F   |

| 1014 00          | WITH HEX NUMBER 7F                                                                              |        |             |

| 1015 7F          |                                                                                                 |        |             |

#### MC6800 BUS & CONTROL SIGNALS

TR1021

## RAM USED FOR STACK STORAGE RAM ADDRESS \$0000-\$007F

# Memory

#### **RANDOM ACCESS MEMORY**

#### RANDOM ACCESS MEMORY (RAM)

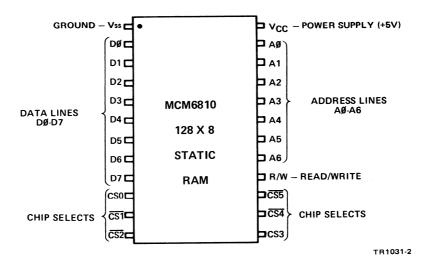

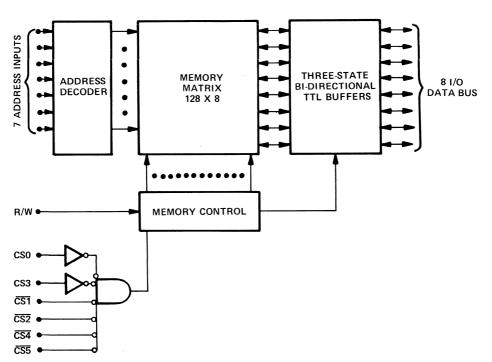

The MCM6810 is a TTL-compatible, static Random Access Memory (RAM). It is a three-state N-MOS chip containing 128 eight-bit words (128 bytes), housed in a 24-pin package. It has 8 data bus pins, 7 address pins, 6 chip select pins (2 active level high, 4 active level low), 2 power pins (ground and +5 V), and a read/write pin.

To access the RAM, all six chip selects must be at their proper levels. The R/W pin must be in a high state to read from the RAM, and in a low state to write into the RAM. When not being accessed, the RAM goes three-state, i.e., high impedance to the data bus. A functional block diagram is shown on the next page.

## MCM6810 RAM FUNCTIONAL BLOCK DIAGRAM

TR1032-2

### **READ ONLY MEMORY**

TR1033

#### **READ ONLY MEMORY (ROM)**

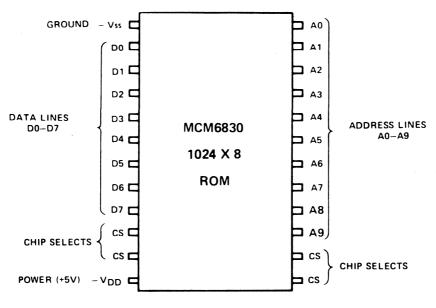

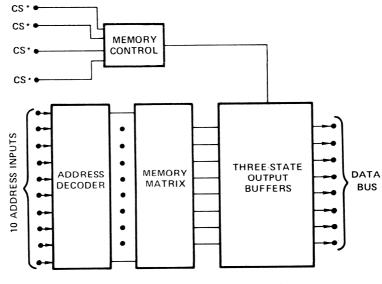

The MCM6830 is a static, TTL-compatible Read Only Memory (ROM). It is a single N-MOS chip containing 1024 eight-bit words (1024 bytes). The ROM is a three-state device housed in a 24-pin package consisting of 10 address pins, 8 data bus pins, 4 chip select pins, and 2 pins for power (+5 V and ground).

The chip selects are defined by the customer (mask programmable) to be either high or low active level.

To access the ROM, all four chip selects must be at their proper levels. When not accessed the device goes three-state, i.e., high input impedance to the data bus.

A functional block diagram is shown on the next page.

## MCM6830 ROM FUNCTIONAL BLOCK DIAGRAM

\*DEFINED BY THE CUSTOMER

TR1034

# M6800 MEMORIES MASK PROGRAMMABLE ROMS

|           |       |                 | tACC  |

|-----------|-------|-----------------|-------|

| MCM68A30  | 1KX8  | +5v             | 350ns |

| MCM6832   | 2KX8  | -5v, +5v, +12v  | 500ns |

| MCM68A308 | 1KX8  | +5v             | 350ns |

| MCM68A316 | 2KX8  | +5v             | 350ns |

| MCM68A332 | 4KX8  | +5v             | 350ns |

| UV        | ERASA | BLE PROMS       |       |

| MCM68708  | 1KX8  | -5v, +5v, +12v  | 450ns |

| MCM2708   | 1KX8  | -5v, +5v, +12v  | 450ns |

| MCM2716   | 2KX8  | – 5v, +5v, +12v | 450ns |

TR1217-2

## M6800 MEMORIES PROMS

|         |                |                |        | <b>tACC</b> |

|---------|----------------|----------------|--------|-------------|

| MC7641  | 512X8          | +5v            | 24 PIN | 85ns        |

| MC7643  | 1KX4           | +5v            | 18 PIN | 85ns        |

|         | S <sup>-</sup> | TATIC RAMS     |        |             |

| MCM6810 | 128X8          | +5 <b>v</b>    | 24 PIN | 450 ns      |

| MCM2114 | 1KX4           | +5v            | 18 PIN | 200ns       |

|         | DY             | NAMIC RAMS     |        |             |

| MCM6604 | 4KX1           | -5v, +5v, +12v | 16 PIN | 250 ns      |

| MCM6605 | 4KX1           | -5v, +5v, +12v | 22 PIN | 200ns       |

| MCM4116 | 16KX1          | -5v, +5v, +12v | 16 PIN | 150ns       |

| MCM4096 | 4KX1           | -5v, +5v, +12v | 16 PIN | 250ns       |

| MCM4027 | 4KX1           | -5v, +5v, +12v | 16 PIN | 150ns       |

TR1217A-2

# PIA

#### PERIPHERAL INTERFACE ADAPTER (PIA) - MC6821

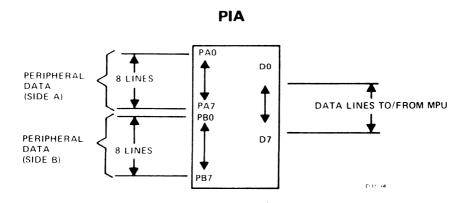

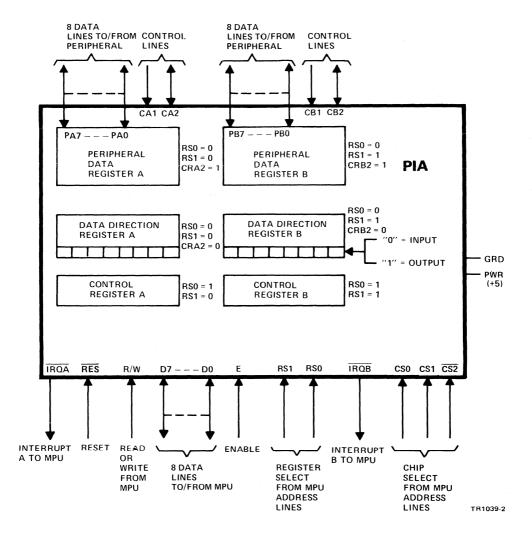

The Peripheral Interface Adapter (PIA) is a means used to interface peripheral equipment with the microprocessing unit (MPU). The PIA communicates with the MPU via an eight-bit bidirectional data bus, three chip selects, two register selects, two interrupt request lines, one read/write line, an enable line, and a reset line. These will be discussed in detail later.

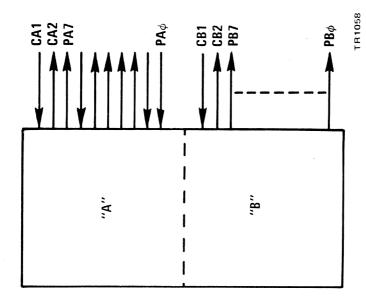

Each PIA has two 8-bit bidirectional peripheral data buses for interfacing with peripheral equipment as shown in Figure 1.

Each peripheral data line may be programmed to act as an input or an output. In addition to the two 8-bit peripheral data buses, peripheral control lines CA2 and CB2 may be programmed to act as a peripheral data line as will be discussed later.

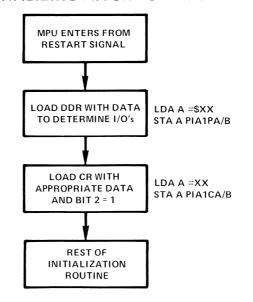

Each PIA consists of two control registers, two data direction registers, and two peripheral interface registers (peripheral data). The control registers and the data direction registers are used to control the data in and out of the PIA.

#### A. PERIPHERAL DATA LINES PA0 through PA7

Each of these 8 data lines which interface with the outside world can be programmed to act as either an input or an output. This is accomplished by setting a "1" in the corresponding bit in the Data Direction Register (DDR) if the line is to be an output—or a "0" in the DDR if the line is to be an input. When the data in the peripheral data lines are read into the MPU by a load instruction, those lines which have been designated as input lines (0 in DDR) will be gated directly to the data bus and into the register selected in the MPU. In the input mode, each line represents a maximum of two standard TTL loads for input high current and 1½ standard TTL loads for a low.

On the other hand, when an output data instruction (STA A PIA) is executed, data will be transferred via the data bus to the peripheral data register. A "1" output will cause a "high" on the corresponding data line and a "0" output will cause a "low" on the corresponding data line (two TTL load drive). Data in Peripheral Register A that have been programmed as outputs may be read by an MPU "LDA A from PIA" instruction. If the voltage is above 2 volts for a logic "1" or below 0.8 volts for a logic "0", the data will agree with that data outputted. However, if these output lines have been loaded such that they do not meet the levels for logic "1", the data read back into the MPU may differ from the data stored in the PIA Peripheral Register A.

#### B. PERIPHERAL DATA LINES PBØ through PB7

The 8 data lines which interface with the outside world on the B side may also be programmed to act either as an input or as an output. This is also accomplished by setting a "1" in the corresponding bit in the Data Direction Register (DDR) if the line is to be an output—or a "0" in the DDR if the line is to be an input. The output buffers driving these lines have three-state capability, allowing them to enter a high-impedance state when the peripheral data line is used as an input. Data in Peripheral Register B that have been programmed as outputs may be read by an MPU "LDA A from PIA" instruction even though the lines have been programmed as outputs. If the line has been programmed as an output and a logic "1", reading the line will indicate a logic "1" regardless of the voltage on the pin, due to buffering between the register and the output pin.

#### C. DATA LINES (DØ through D7)

The 8 bidirectional data lines permit transfer of data to/from the PIA and the MPU. The MPU receives data from the outside world from the PIA via these 8 data lines, or sends data to the outside world through the PIAs via the 8 data lines. The data bus output drivers are three-state devices that remain in the high-impedance (off) state except when the MPU performs a PIA read operation.

#### D. CHIP SELECT LINES (CSØ, CS1, CS2)

These are the lines which are tied to the address lines of the MPU. It is through these lines that a particular PIA is selected (addressed). For selection of a PIA, the CSØ and CS1 lines must be high and the  $\overline{\text{CS2}}$  must be low. After the chip selects have been addressed, they must be held in that state for the duration of the E (enable) pulse, which is the only timing signal supplied by the MPU to the PIA. This enable pulse (E) is normally the  $\phi 2$  clock. One of the address lines should be ANDed with the VMA line with this output tied to a chip select.

#### PIA-4 Peripheral Interface Adapter (MC6821)

#### E. ENABLE LINE (E)

The enable pulse (E) is the only timing signal that is supplied to the PIA by the MPU. Timing on all other signals is referenced to the leading or trailing edges of the E pulse.

#### F. RESET LINE (RS)

This line is used to reset all registers in the PIA to a logical zero. This would be used primarily during a reset or power-on operation. This line is normally in the high state. A low level resets all registers in the PIA.

#### G. READ/WRITE LINE (R/W)

This signal is generated by the MPU to control the direction of the data transfers on the data bus. A low state on the PIA Read/Write line enables the input buffers and data is transferred from the MPU to the PIA (MPU write) on the falling edge of the E ( $\phi$ 2) signal if the device has been selected. A high on the Read/Write line sets up the PIA for a transfer of data to the data bus (MPU read). The PIA output buffers are enabled when the proper address and the enable pulse are present, thus transferring data to the MPU.

#### H. INTERRUPT REQUEST LINES (IRQA and IRQB)

These lines are used to interrupt the MPU either directly or indirectly through interrupt priority circuitry. These lines are "open source" (no load device on the chip) and are capable of sinking a current of 1.6 mA from an external source. This permits all interrupt request lines to be tied together in a "wire OR" configuration. Interrupts are serviced by a software routine that sequentially reads and tests, on a prioritied basis, the two control registers in each PIA for interrupt flag bits (Bit 6 and 7) that are set. Discussion on the control registers and how the flag bits get set will follow. When the MPU reads the Peripheral Data Register, the Interrupt Flags (Bit 6 and Bit 7) are cleared and the Interrupt Request is cleared.

These request lines (IRQA and IRQB) are active low.

#### I. INTERRUPT INPUT LINES (CA1 and CB1)

These lines are input only to the PIA and set the interrupt flag (Bit 7) of the control registers in the PIA. Discussion of these lines in conjunction with the control register will follow.

#### J. PERIPHERAL CONTROL LINE (CA2)

This line can be programmed to act either as an interrupt input or as a peripheral output. As an output, this line is compatible with standard TTL, (2 load drive) and as an input represents two standard TTL loads for input high current and 1½ standard TTL loads for a low. The function of this line is programmed with Control Register A (Bits 3, 4, and 5).

#### K. PERIPHERAL CONTROL LINE (CB2)

This line may also be programmed to act as an interrupt input or as a peripheral output. As an input, this line has greater than 1 megohm input impedance and is compatible with standard TTL. As an output, it is compatible with standard TTL (2 load drive) and may also be used as a source of up to 1 milliamp at 1.5 volts to directly drive the base of a transistor switch. The function of this line is programmed with Control Register B (Bits 3, 4, and 5).

#### CONTROL REGISTER A (CRA)

| 7     | 6     | 5 | 4           | 3 | 2    | 1     | Ø      |

|-------|-------|---|-------------|---|------|-------|--------|

| IRQA1 | IRQA2 | C | CA2 Control |   | DDRA | CA1 C | ontrol |

#### CA 1 Control (Bits Ø and 1)

Peripheral control line CA1 is an input-only line which may be used to cause an interrupt by setting the interrupt flag IRQA1 (Bit 7) of Control Register A (CRA). Bits Ø and 1 of CRA are used to determine how the interrupt is to be handled.

After the MPU reads Peripheral Data Register A, the IRQA1 and IRQA2 (Bits 6 and 7) will be cleared.

PIA-6 Peripheral Interface Adapter (MC6821)

| Transition of<br>Interrupt<br>Input Line CA1 | Status of<br>Bit 1 in<br>CRA (Edge) | Status of<br>Bit Ø in<br>CRA (Mask) | IRQA1<br>(Interrupt Flag)<br>Bit 7 of CRA | Status of IRQA Line (MPU Interrupt Request) |

|----------------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------------|---------------------------------------------|

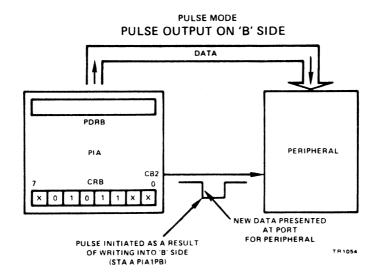

|                                              | 0                                   | 0                                   | 1                                         | MASKED<br>(Remains High)                    |